Voices: CriticalBlue's David Stewart Pg 20

Transimpedanceamplifier-noise issues Pg 22

Prying Eyes: Artificial cochlea Pg 24

Design Ideas Pg 55

Tales from the Cube: Good as gold Pg 66

HIDS-ON AD

## VIRTUALIZATION: SILICON AND SOFTWARE SALVATION OR TECHNOLOGICAL TOWER OF BABEL?

Page 34

### **ON TIME, EVERY TIME:** EMBEDDING REAL-TIME PERFORMANCE

Page 27

### EXTENDING SPI4.2 CAPABILITIES FOR ETHERNET SERVICES

Page 47

CLICK HERE TO **RENEW** your FREE magazine subscription CLICK HERE TO **START** a FREE <u>e-newsletter</u> subscription Ĵ

## The New Oscilloscope Experience Is Here

## Quick Insight. Deep Insight.

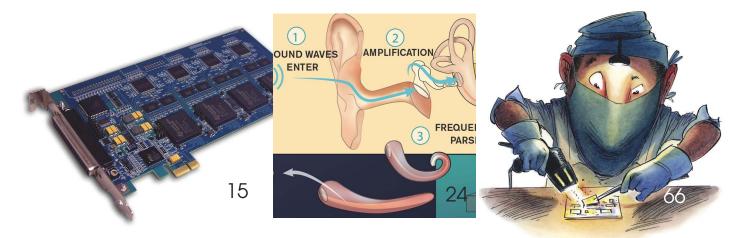

Experience the New LeCroy Oscilloscopes.

www.insightwithconfidence.com

www.lecroy.com

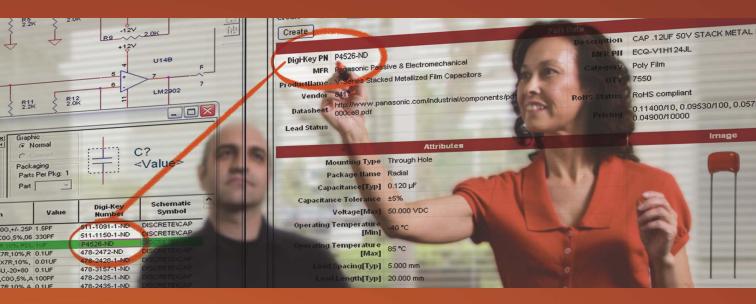

# YOUR SOURCE FOR Semiconductors

Visit www.digikey.com for the industry's broadest selection of semiconductors!

**Digi-Key Corporation purchases all product**

directly from its original manufacturer.

Quality Electronic Components, Superior Service

\*New product added daily. © 2008 Digi-Key Corporation

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

### Hammer Down Your Power Consumption with picoPower™!

## **THE Performance Choice for Lowest-Power Microcontrollers**

Performance and power consumption have always been key elements in the development of AVR<sup>®</sup> microcontrollers. Today's increasing use of battery and signal line powered applications makes power consumption criteria more important than ever. To meet the tough requirements of modern microcontrollers, Atmel<sup>®</sup> has combined more than ten years of low power research and development into picoPower technology.

picoPower enables tinyAVR®, megaAVR® and XMEGA<sup>™</sup> microcontrollers to achieve the industry's lowest power consumption. Why be satisfied with microamps when you can have nanoamps? With Atmel MCUs today's embedded designers get systems using a mere 650 nA running a realtime clock (RTC) and only 100 nA in sleep mode. Combined with several other innovative techniques, picoPower microcontrollers help you reduce your applications power consumption without compromising system performance!

Visit our website to learn how picoPower can help you hammer down the power consumption of your next designs. PLUS, get a chance to apply for a free AVR design kit!

### http://www.atmel.com/picopower/

Automotive Sensors **Circuit Protection Solutions** Magnetic Products Microelectronic Modules Panel Controls & Encoders Precision Potentiometers Resistive Products

## How Will You Protect Your Circuits?

Circuit protection is a crucial part of any design decision today. No one understands that better than Bourns. We have developed the industry's broadest line of circuit protection solutions – backed by a global team of technical experts. Our customers are assured of finding the optimal solution for their application with Bourns' collective knowledge from years of circuit protection support. Beyond product depth and support, we have innovative new technologies that solve tough design challenges. Bourns' new gated thyristors provide faster and more efficient protection that reduces costs. Our symmetric gas discharge tubes regulate breakdown voltage innovatively. And Bourns' new polymer PTCs overcome voltage variability to extend product life. In the New World of Bourns, we have the technology to protect your circuits.

www.bourns.com/circuitprotection

Bourns - the company you have relied on for more than 60 years.

Built on Trust...Based on Innovation

## Green Engineering Powered by National Instruments

MEASURE IT

Acquire environmental data from thousands of sensors

Analyze power quality and consumption

Present measured data to adhere to regulations

FIX IT

Design and model more energy efficient machines

Prototype next-generation energy technologies

Deploy advanced controllers to optimize existing equipment

For more than 30 years, National Instruments has empowered engineers and scientists to measure, diagnose, and solve some of the world's most complex challenges. Now, through the NI graphical system design platform, engineers and scientists are using modular hardware and flexible software to not only test and measure but also fix inefficient products and processes by rapidly designing, prototyping, and deploying new machines, technologies, and methods. Today, a number of the world's most pressing issues are being addressed through green engineering applications powered by NI products.

>> Download green engineering resources at ni.com/greenengineering

### 800 890 1345

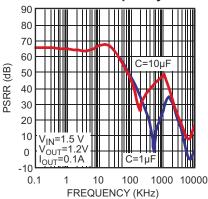

### EDN HANDS-ON PROJECT: Virtualization: silicon and software salvation or technological tower of Babel?

34 Stable, robust code speaks one language; new CPUs speak another. Is a software rewrite necessary to resolve the seeming contradiction, or can virtualization temporarily—or even permanently—ease the translation?

by Brian Dipert, Senior Technical Editor

### On time, every time: embedding real-time performance

27 High-speed graphics, user interfaces, and networks represent the norm in embedded-system designs, and these performance issues dictate the use of multitasking firmware. by Warren Webb, Technical Editor

# **EDN** contents 10,2,08

### Extending SPI4.2 capabilities for Ethernet services

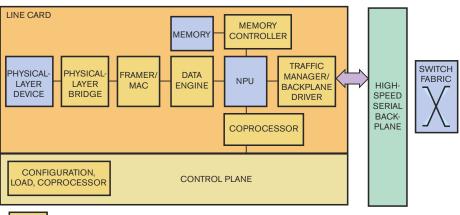

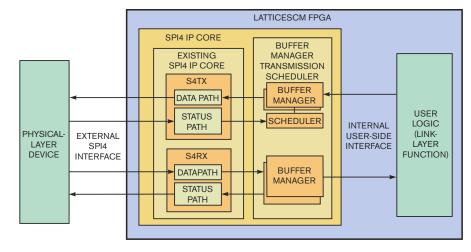

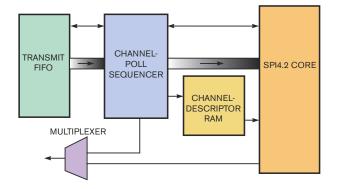

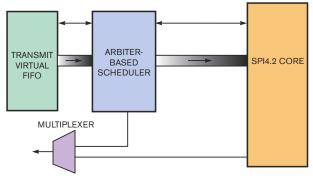

477 With the proliferation of Internet Protocolbased systems in the telecommunications market, designers are turning to FPGAs to create intelligent Ethernet bridges and traffic managers.

by Shakeel Peera, Lattice Semiconductor

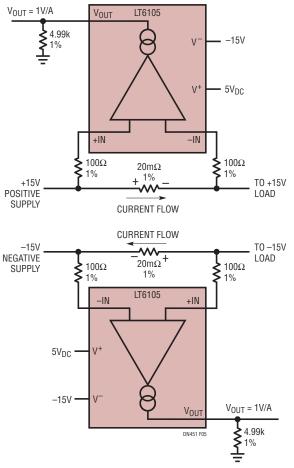

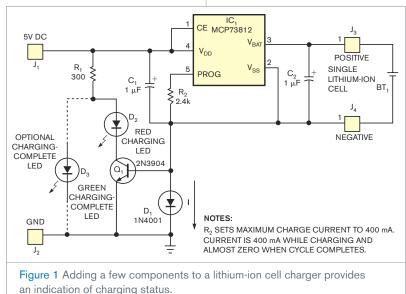

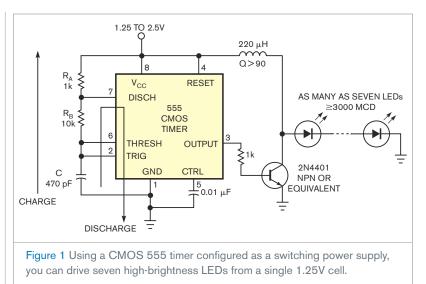

## DESIGNIDEAS

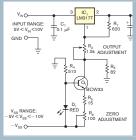

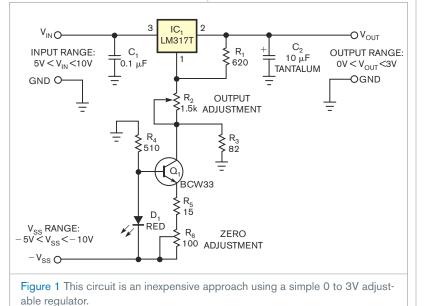

- 55 Use an LM317 as 0 to 3V adjustable regulator

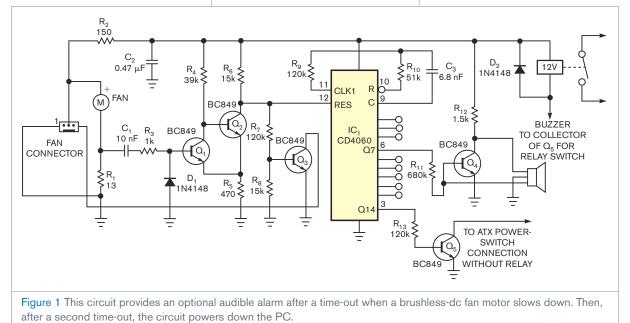

- 56 Alarm monitors rotational speed of dc motor

- 58 Add charging status to a simple lithium-ion charger

- 58 555 timer drives multiple LEDs from one NiMH cell

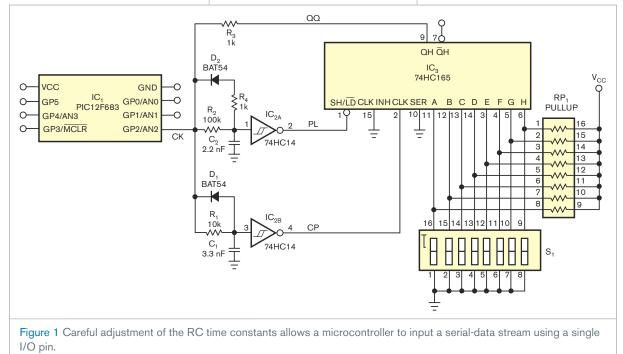

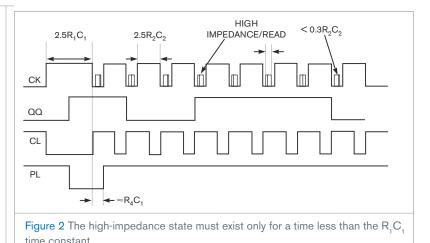

- 60 Microcontroller inputs parallel data using one pin

### WHAT DO WE HAVE TO DO, DRAW YOU A PICTURE?

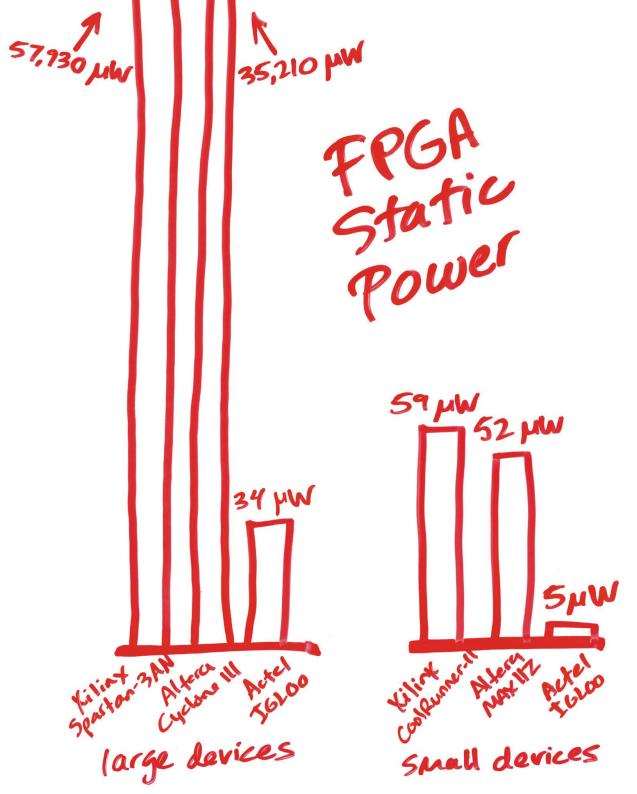

Only Actel gets you this close to zero. Any other claims of low power superiority are just that. According to their own data, Altera<sup>®</sup> and Xilinx<sup>®</sup> use between 10 and 1700 times the power of Actel IGLOO<sup>®</sup> FPGAs, depending on device and mode. Want specifics? Visit us to get the whole picture, including a video of actual measurements.

## **contents** 10.2.08

- 16 Analyzer/exerciser validates 5-Gbps SuperSpeed USB 3.0

- 18 Automotive EEPROMs use two cells per bit for ruggedness, reliability

- 18 Henry Ott EMC seminar, San Francisco, Oct 15 to 17

- 20 Voices: CriticalBlue's David Stewart

## DEPARTMENTS & COLUMNS

- 10 EDN.comment: Why tout a demo board nobody can buy?

- 22 Baker's Best: Transimpedance-amplifier-noise issues

- 24 **Prying Eyes:** Artificial cochlea: an example of structural processing

- 66 Tales from the Cube: Good as gold

## PRODUCT ROUNDUP

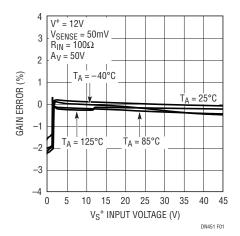

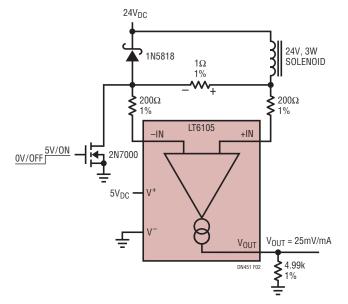

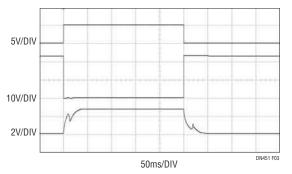

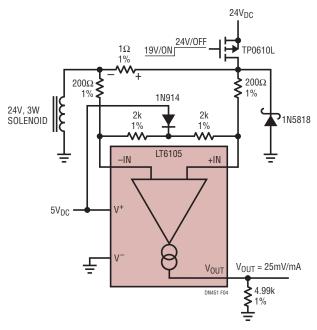

64 Amplifiers, Oscillators, and Mixers: Currentsensing amplifiers, autozero-operation amplifiers, dual ADC drivers, low-power comparators, and more

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80129 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box, 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box, 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box, 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box, 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2008 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issue: US, \$165 one year; Canada, \$226 one year (includes 7% GST, GST#123397457), Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian address to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 53, Number 20 (Printed in USA).

# The Newest Optoelectronics

**Over A Million Products Online**

### New Products from:

PCB PolyLEDs www.mouser.com/ avagotechnologies/a

#### Led Engin, Inc. 10W RGB LED Emitters www.mouser.com/ ledengin/a

XcelLed™ 1W Emitters www.mouser.com/ everlight/a

**EVERLIGHT**

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 366 leading suppliers.

a tti company

The Newest Products For Your Newest Designs

(800) 346-6873

# EDN at edn.com

EXPANDED ENGINEERING COVERAGE PLUS DAILY NEWS, BLOGS, VIDEO, AND MORE.

### ONLINE ONLY

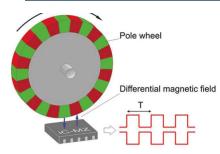

Check out these Web-exclusive articles: **Speed acquisition made simple** Speed acquisition is of central importance in the control and monitoring of motion processes. You can simply and efficiently tackle the task using magnetic sensors based on the Hall principle. → www.edn.com/article/CA6594313

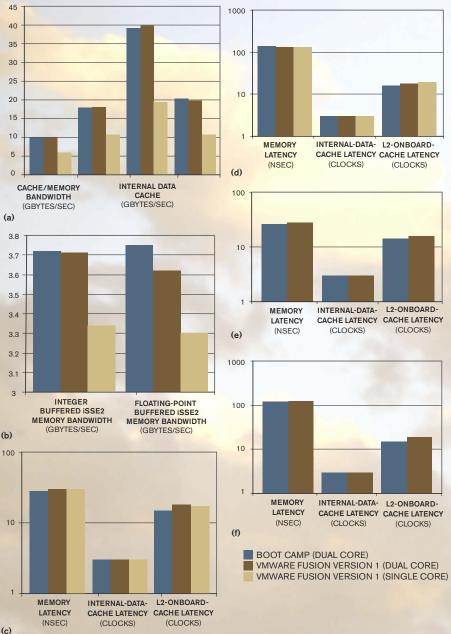

## Challenges and design decisions for measuring multicore performance

The type of multicore processor you choose and the type of parallelism you apply in your application code will greatly affect the performance you will achieve. To ensure that you meet your goals, closely examine the benchmark scores produced by an industry-standard suite of multicore benchmarks.

→www.edn.com/article/CA6592752

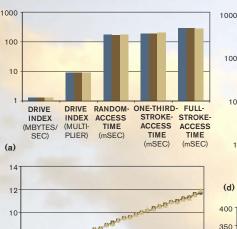

#### The hard-drive click of death: archaic technologies and their protracted viabilities

Why are we still using rotating magnetic mass storage that's powered by a motor spinning at 4200, 5400, 7200, or 10,000 rpm, with a rapidly vacillating read/write head suspended only a few millionths of an inch above its platter mate? →www.edn.com/081002toc1

### **HOT TOPICS**

Check out *EDN*'s new Hot Topics pages: From WiMax to H1-B visas to automotive electronics, Hot Topics pages deliver continuously updated subject-specific links from not only *EDN* but also the entire electronicsindustry Web.

→www.edn.com/hottopics

### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

Prying apart a portable audio player A look inside Sandisk's Sansa M250 reveals platform-minded design decisions, surprising flash-memory choices, and potential hacks.

→www.edn.com/article/CA6590195

### Lithium-ion technology targets portable power

→www.edn.com/article/CA6586222

MIT researchers use plant-energy-storage system for solar-storage innovation →www.edn.com/article/CA6583673

Handcrafted analog gets automated assist →www.edn.com/article/CA6590188

Transimpedance-amplifier stability is key in light-sensing applications →www.edn.com/article/CA6590187

If you can't beat patent trolls, join them

→www.edn.com/article/CA6594114

### THE IC INSIDER

Get a peek inside the latest ICsliterally-courtesy of *EDNs* new online feature, The IC Insider. This monthly exclusive, contributed by reverse-engineering company Chipworks, couples actual silicon imagery with circuit schematics and pro-

##

vides a technical INSIDER discussion of some of the innovative

features of a recently introduced IC. The premiere installment looks at Maxim's MAX8814ETA battery-charger chip. →www.edn.com/icinsider

## High Density and High Performance

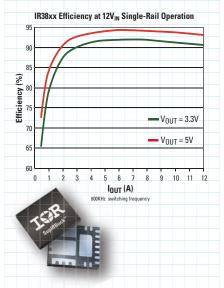

IR's Sup/RBuck™ Integrated Regulators deliver benchmark efficiency for data center and consumer applications

#### SupIRBuck Advantages:

- Integrates IR's high performance synchronous buck control ICs and benchmark HEXFET<sup>®</sup> trench technology MOSFETs

- 8-10% higher efficiency compared to monolithic Power IC two-stage solution

- High density compared to

equivalent discrete solution

#### For more information call 1 800 981 8699 or visit us at www.irf.com/dcdc

### BY PAUL RAKO, TECHNICAL EDITOR

## Why tout a demo board nobody can buy?

ecently, my buddy Dave was trying to make a remote-control airplane that would transmit high-definition video to the operator on the ground. Because he wanted to use the video in real time to control the plane, he needed a system with minimal latency. This requirement caused Dave to consider systems that transmit uncompressed video. Dave had been exploring a lot of technologies, and one that caught his eye was a chip set from Amimon. The chip set transmits high-definition video as a 40-MHz-wide signal in the 5.8-GHz ISM (industrial/

scientific/medical) band. The company targets this chip set for use in consumer electronics because every TV and output device, including DVD players and set-top boxes, can handle uncompressed video.

Amimon's Web site lists not only the chip set, but also both a module and a demo board. Dave contacted the company regarding the price of the demo board, but the company refused to provide it. I then wrote to the company and asked the price. The company's public-relations agency responded: "There is no set pricing for the development kits; it depends on vendor needs." Dave needed a free one but realized that he couldn't qualify for a free sample because he was just at the hobby stage.

Weeks later, Dave e-mailed me. "I got an e-mail reply from Amimon," he wrote, stating that he had received the same response as the one I had received. "They asked "What would be the cooperation model with Amimon?" Huh? There must be some supersecret marketing-indoctrination cult ... that

My friend Dave is "dreaming of a day when 'call for pricing' and 'contact your local rep' will be banned from industrial suppliers' Web sites."

screws up people's minds so completely that they cannot speak in plain English. Put the darned development kit on Digi-Key for \$800, and I'll buy it!" He went on to point out that many companies, including National Semiconductor, Linear Technology, Fairchild, Texas Instruments, and Analog Devices, all put their demo boards up for sale through distributors such as Digi-Key. "I'm dreaming of a day," he continued, "when 'call for pricing' and 'contact your local rep' will be banned from industrial suppliers' Web sites."

I believe that all this turmoil probably derives from the fact that marketing types and engineers speak different languages. Marketing types are dying to talk to people, go to lunch, and network. Engineers, on the other hand, want to crawl into a corner with some hardware and be alone. Industrial suppliers Digi-Key, Mouser, Newark, and Jameco have made things a lot better than they were a decade ago, though, when most manufacturers insisted that you contact the factory for samples, and the big distributors only wanted to sell you a reel of 4000 parts.

The marketing types are trying to uncover the next high-volume-sales opportunity so that they can schmooze with you and beat their competitors. When engineers are producing prototypes, however, they have neither the time nor the inclination for all this socializing. The last system board I designed, a point-of-sale terminal, had 100 parts and 20 ICs. If every manufacturer had required me to call and undergo qualification just to get two bucks' worth of samples, it would have taken a month. With only two months to design and build the whole product, this approach would have been unfeasible.

How about you? Do you hate the fact that manufacturers won't give you a price and don't sell small quantities through distribution? Sound off at *EDN*'s Web site, www.edn.com/ 081002ed.EDN

Contact me at paul.rako@edn.com.

+ Go to www.edn.com/081002ed and click on Feedback Loop to post a comment on this column.

+ More at www.edn.com/edncomment

## 29 More Q. Less Cu

## These tiny new air core inductors have the highest Q and current handling in the smallest footprint.

Coilcraft's new SQ air core inductors have unmatched Q factors: most are above 200 in the 1-2 GHz range! That's 3 times higher than comparably sized 0805 chip coils.

←1.83 mm→

RDER DIRECT

COILCRAFT.COM BOO-322-2645

And with their extremely low DCR, they can handle 4 to 8 times more current: up to 4.4 Arms.

SQ air core inductors are perfect for your LC filter and RF impedance matching applications. They come in 15 values ranging from 6 to 27.3 nH, all with 5% tolerance.

standard chip inductors

These coils

are significantly smaller than existing air core inductors. We reduced the footprint by using close-wound construction and keeping the leads close to the body. The square shape cuts the height to as low as 1.5 mm and creates flat top and bottom sur-

faces for easy automated handling and stable mounting.

The square shape and narrow footprint reduce board space by 60-75% over conventional air core inductors.

See how the ultra-high Q and current handling of Coilcraft's new SQ air core inductors can

maximize the performance of

your next design. For complete specifications and free evaluation samples, visit www.coilcraft.com/sq

Coilcraft

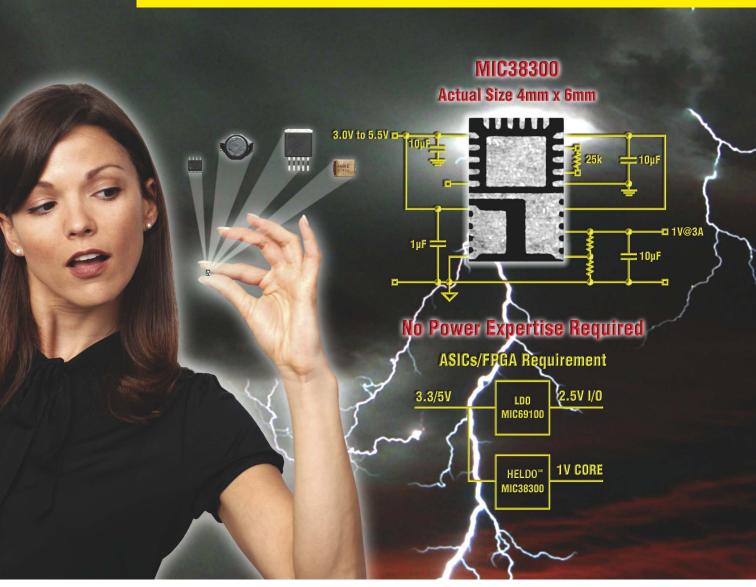

## Power That Gives You The Best Of Both Technology Worlds

### Switcher Efficiency Combined With LDO Noise And Transient Performance

The **MIC38300** is a 3A step down converter and the first device in a new generation of HELDO<sup>TM</sup> products providing the benefits of LDOs with respect to ease of use, fast transient performance, high PSRR and low noise while offering the efficiency of a switching regulator.

As output voltages move lower, the output noise and transient response of a switching regulator become an increasing challenge for designers. By combining a switcher whose output is slaved to the input of a high performance LDO, high efficiency is achieved with a clean low-noise output.

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/mic38300.

### The Good Stuff:

- 2.2A Continuous operating current

- ◆ Input voltage range: 3.0V to 5.5V

- Adjustable output voltage down to 1.0V

- Output noise less than 5mV

- Ultra fast transient performance

- Unique Switcher plus LDO architecture

- Fully integrated MOSFET switches

- Micro-power shutdown

- Easy upgrade from LDO as power dissipation becomes an issue

- Thermal shutdown and current limit protection

- ◆ 4mm × 6mm × 0.9mm MLF <sup>®</sup> package

#### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark.finkelstein@reedbusiness.com; 1-781-734-8431

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-408-345-4437; judy.hayes@reedbusiness.com

VICE PRESIDENT, EDITORIAL DIRECTOR Karen Field, 1-781-734-8188; kfield@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-781-734-8418; melson@reedbusiness.com

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com

Contact for contributed technical articles EDITOR-IN-CHIEF, EDN.COM Matthew Miller 1-781-734-8446; fax: 1-303-265-3017;

mdmiller@reedbusiness.com SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187;

bdipert@edn.com MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116;

rcravotta@edn.com **NEWS** Suzanne Deffree, Managing Editor

1-631-266-3433; sdeffree@reedbusiness.com **POWER SOURCES, ONLINE INITIATIVES** Margery Conner, Technical Editor

1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

SEMICONDUCTOR MANUFACTURING AND DESIGN Ann Steffora Mutschler, Senior Editor

1-408-345-4436; ann.mutschler@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-303-265-3131;

f.granville@reedbusiness.com ASSOCIATE EDITOR Maura Hadro Butler, 1-617-276-6523;

mbutler@reedbusiness.com EDITORIAL/WEB PRODUCTION

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042 CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net

Nicholas Cravotta, editor@nicholascravotta.com

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn; Pallab Chatterjee PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164

Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-303-265-3015

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA Susie Newham, Managing Director susie.newham@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@idg-tbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

> DENNIS BROPHY Director of Business Development, Mentor Graphics

DANIS CARTER Principal Engineer, Tyco Healthcare CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV

System Architect, Intel RON MANCINI Retired Staff Scientist GABRIEL PATULEA

Design Engineer, Cisco

Product Line Director, Analog Devices SCOTT SMYERS

VP Network and System Architecture Division, Sony

TOM SZOLYGA Program Manager, Hewlett-Packard JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@readbusiness.com. For a free subscription, go to www.geffreemag. com/edn. Read Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

## **MAXIMUM** PRECISION

### **From a full spectrum of pin receptacles** Regardless of whether your components fly with the Blue Angels or control industrial robots, good design should never be limited by a lack of options. Mill-Max Mfg. Corp. offers hundreds of high-precision receptacle styles with an unprecedented range of options and features:

- 35 pre-tooled contact styles.

- A full selection of 3-, 4- and 6-finger contact designs.

- .008" to .102" (0,20 2,59mm) pin acceptance.

- Accepts round, square and rectangular component leads.

- Styles for soldering, swaging or press-fitting.

Large Variety of Styles

Knock-out Bottom OFP®

Available on Tape and Reel

Mill-Max receptacles. Plug into the simple, reliable connectivity solution.

To view our Design Guide, new product offerings and order free samples, visit

www.mill-max.com/EDN585

See for Yourself at www.xilinx.com/spartan

### GET UP TO 50% LOWER COST

- Integrated features and only two power rails minimize need for external components

- Save up to 70% in logic cell resources with dedicated DSP blocks

- Run cool with 11mW static power,  $0\mu W$  in hibernate mode

In the highly competitive high-volume market, cost is king. Our latest Extended Spartan®-3A FPGAs deliver the integrated features, low static power, complex computation and embedded processing capabilities you need to achieve the absolute lowest total cost. Period.

Combine these advantages with the industry's largest selection of IP cores, reference designs and I/O standards and you have the most complete low-cost programmable solution available for your next high-volume design.

Visit us at **www.xilinx.com** to download our free ISE<sup>®</sup> WebPACK<sup>™</sup> design tools and start saving money today.

### EDITED BY FRAN GRANVILLE

### **INNOVATIONS & INNOVATORS**

### Video card captures 480 frames/sec

xtending its line of OEM video-capture cards, Sensoray recently announced the model 817 PCIe (peripheral-component-interconnect-express) frame-grabber card, which captures 16 channels of compressed JPEG or uncompressed bit maps at speeds as high as 480 frames/sec. Supporting one, four, eight, or 16 PCIe slots, the board

The Sensoray model 817 PCIe frame grabber captures 16 video channels of compressed JPEG or uncompressed bit maps at 480 frames/sec. allows the user to set independent capture parameters for each channel. An internal  $16 \times 4$  analog cross-point-video switch routes any combination of four input channels to external video monitors. Users can turn each of the four video outputs on or off, allowing the outputs of multiple cards to drive one monitor.

The model 817 contains four identical VCPUs (video-capture and -processing units), each of which handles four input-video channels. Each VCPU employs a four-channel video decoder to convert analog video into digital and a DSP to capture digitized video and to handle various processing tasks, such as frame decimation, caption overlay, JPEG compression, and status reporting. Sensoray provides a software-development kit for the module

that includes drivers and sample applications for Windows and Linux operating systems. The price for the model 817 starts at \$705 (OEM quantities).—by Warren Webb >Sensoray, www.sensoray.com. FEEDBACK LOOP

"I've found that

reproducing the

failure is half

of the problem,

and, usually, ...

the logistics of

implementing the

fix are the other

half."

-Reader Ron Bauerle, in *EDN*'s Feedback Loop, at www.edn. com/article/CA6578156. Add your comments.

### Book helps you resolve BGA-layout issues

As a circuit designer who also often lays out quite complex boards, I found the temptation to purchase Charles Pfeil's new book-BGA Breakouts & Routing: Effective Design Methods for Very Large BGAsirresistible, and I wasn't disappointed. The approximately 160 pages and more than 100 figures within this quality paperback carry a wealth of information that far exceeds what I've amassed during my attempts over the past seven years that I've been designing with BGA (ball-grid-array) packages. And, at approximately \$31, this invaluable information comes cheap.

Although Pfeil is engineering director at Mentor's system-design division and the colorful, instructive screenshots that adorn virtually every page originate from his company's products, this is no selfserving, Mentor-driven publicity exercise. Rather, it is a usable resource that tackles PCB (printed-circuit-board) designers' problems as BGA packages become ever denser.

The first two chapters explain BGA-specific concepts, terminology, and packages. In-depth discussions of HDI (high-density-interconnect)-layer stackups, fan-out patterns, and layer-biased breakouts follow. The author concludes with a chapter that explores alternative approaches to routing a 1760-ball device on a 0.8-mm pitch. This exercise gives great insight about how well different approaches may work for you, even with the smaller BGA packages that most designers use.—**by David Marsh**

Mentor Graphics,

www.mentor.com/go/bga.

## pulse

## Analyzer/exerciser validates 5-Gbps SuperSpeed USB 3.0

Ithough USB (Universal Serial Bus) 3.0 with its 5-Gbps SuperSpeed technology probably won't reach the market in volume until mid-2010, manufacturers are now developing computers and peripheral devices employing the new bus. To work on these products and their all-important supporting software-especially drivers-engineers need tools for exercising developmental devices and software, analyzing bus performance, ensuring compatibility with earlier versions of USB, and debugging flaws. According to LeCroy Corp, the needed tools weren't commercially available until its August introduction at the Intel Developer Forum (www.intel. com/idf) in San Francisco of the Voyager validation system, which LeCroy describes as the

first protocol analyzer/exerciser for USB 3.0.

Using custom front-end circuits, which the company developed for its 5-Gbps PCle (peripheral-component-interconnect-express) analyzer/ exerciser, the instrument performs simultaneous protocol capture of USB 2.0 and 3.0 signaling. An integrated exerciser option enables the sixthgeneration unit to completely test and validate the performance of USB devices, systems, and software.

Engineers often refer to USB 3.0's SuperSpeed mode as more than 10 times as fast as USB 2.0's high-speed mode. That characterization may or may not be valid. SuperSpeed operation uses 8-bit/10-bit coding, which reserves 20% of the transmitted bits for error correction, thus allowing the 5-

Gbps data stream to transmit a maximum of 4 Gbps of real data. The USB 2.0 high-speed mode, which does not incorporate error correction, can transmit bursts of data at 480 Mbps, or 12% of 4 Gbps. In sustained operation, however, the maximum high-speed-mode data rate is closer to 300 Mbps. Because the SuperSpeed protocol may prove more efficient than the high-speed protocol, USB 3.0 may more than compensate for its error-correction overhead.

Another feature of USB 3.0 is adaptive equalization, which optimizes a link's output waveshape in response to training sequences that run automatically when you establish a new connection. Unlike buses that mainly find use in backplanes, USB is primarily a cabled bus. Because such

LeCroy calls the Voyager validation system the first protocol analyzer/exerciser for 5-Gbps USB 3.0. The unit supports simultaneous USB 2.0 and 3.0 data capture, which is necessary for testing USB 3.0 hubs.

### **DILBERT By Scott Adams**

buses use cables of unpredictable length and because waveform distortion depends strongly on path length, adaptive equalization is essential to achieving the advertised data rate.

LeCroy regards the situation with USB 3.0 connectors as potentially still fluid. Whereas manufacturers have designed and prototyped connector types that are close to receiving approval from the USB Implementers Forum (www.usb. org), modified or added types are still possible. Therefore, the company designed the Voyager system to make it easy for users to change the bus connectors. Users can substitute SMA connectors for USB connectors if the "real" connectors are temporarily unobtainable.

USB 3.0 will be backwardcompatible with USB 2.0 but in a different way from the way that USB 2.0 is backward-compatible with USB 1.1. USB 2.0 cables mate and work with USB 1.1 connectors. USB 3.0 devices will have connectors that mate with both USB 2.0 and USB 3.0 cables, but, if you want to use a USB 3.0 device in a system based on USB 2.0, you will need a USB 2.0 cable, which may be an optional accessory to the USB 3.0 device. According to LeCroy, testing of USB hubs will make it nearly essential that USB 3.0 analyzer/exercisers support simultaneous USB 2.0 and 3.0 data capture.

LeCroy says that fiber-optic implementations are likely to emerge in the future but that initial implementations will use copper cables. US prices for the Voyager system begin in the \$20,000 to \$30,000 range.-by Dan Strassberg >LeCroy Corp, www.lecroy. com.

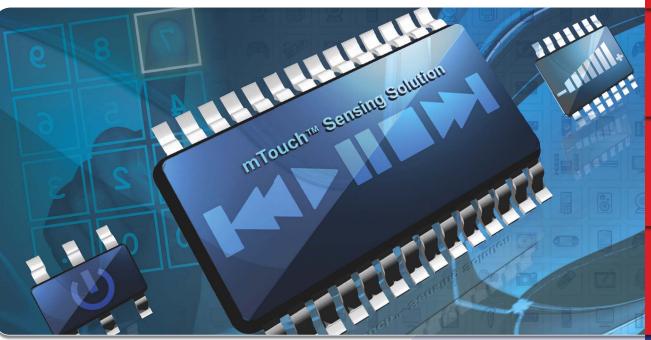

## Capacitive Touch Sensing In a Flexible, Single-chip Solution

Capacitive touch interfaces provide an excellent way to add low-cost, reliable and stylish buttons into your design. Microchip Technology's mTouch<sup>™</sup> Sensing Solution includes comprehensive development kits and a free diagnostic tool to make implementation easy and fast. Our free source code can be seamlessly integrated with your existing firmware on a single PIC<sup>®</sup> microcontroller – eliminating the need for additional controllers.

### THE mTouch SENSING SOLUTION FEATURES:

- FREE license libraries and source code

- A FREE diagnostic tool

- Integration with 8- and 16-bit PIC microcontrollers

- Easy expansion, with support from 6 to 100 pins

- Low-power operation

### **GET STARTED IN 3 EASY STEPS**

Microcontrollers

Digital Signal Controllers

Analog

Serial EEPROMS

- Visit the mTouch Sensing Solutions design center at www.microchip.com/mTouch

- 2. Download FREE libraries and source code

- For a limited time, save 20% off a variety of touch sensing development tools when you purchase from www.microchipDIRECT.com and use coupon code mTouch4U.

## pulse

## Automotive EEPROMs use two cells per bit for ruggedness, reliability

ith the aim of ensuring reliable operation and long life in the demanding automotive environment, Rohm has introduced a series of EEPROMs that employ a double-cell structure. The BR25Hxx0 devices, which are SPI (serial-peripheral-interface)-bus memories, withstand the voltage surges, static discharge, heat, and vibration that they may encounter in automotive ECUs (engine-control units). Features include guaranteed operation at 125°C, with 20-year data retention at 85°C,

6-kV ESD (electrostatic-discharge) resistance, gold-pad/ gold-wire connections, and a double-reset function for high reliability. The devices' high-redundancy circuits and a choice of process technology allow the company to specify a life of 1 million rewrites at 85°C and 300,000 rewrites at 125°C.

EEPROMs are increasingly finding use in critical automotive systems to record, for example, status information. As most users know, the devices also have a wear-out mechanism; charge is transferred by charge tunneling across an oxide barrier. Eventually, on a lifetime-related but somewhatrandom basis, the oxide in a cell may break down. Rohm addresses this breakdown by fabricating two identical but separate memory cells for each bit and connecting them in an OR configuration, so that the combined cell will continue to function after a failure.

To protect against error conditions during power-up or voltage dips, the EEPROMs integrate a double-protection circuit comprising a POR (power-on-reset) block that resets during start-up of the power source and a low-voltage write-error-correction circuit that resets the internal circuit and prohibits write operations in low-voltage conditions.

Rohm produces variants with Microwire, I<sup>2</sup>C (inter-integratedcircuit), and SPI interfaces; the 5-MHz SPI is the fastest. The 14 devices in the family come in  $6.2 \times 5 \times 1.71$ -mm SOP-8 and  $6 \times 4.9 \times 1.75$ -mm SOP-J8 packages and in capacities of 1, 2, 4, 8, 16, and 32 kbits. The memories support high-speedwrite and page-write modes.

-by Graham Prophet ► Rohm Electronics, www.rohm.com.

## NBLOG

ANABLOG

## Henry Ott EMC seminar, San Francisco, Oct 15 to 17

I just got a flyer from Henry Ott about a three-day seminar on electromagnetic-compatibility engineering (www.hottconsul tants.com/emccourse\_3-day. html). Cost is \$1375. Henry is a former Bell Labs researcher that really understands signal integrity, EMC, and RFI issues in your design. He has done great work in figuring out layout issues on PCBs.

I have blogged before about Henry's assertion that

you should not cut up ground planes. I wholeheartedly agree; it usually causes more problems than it solves. The whole cutting-up-the-

plane suggestion came from application engineers working at semiconductor companies, who never had to get a whole system working. The ADC guys would plop an ADC on an evaluation board and warn you to separate the analog and digital grounds. Easy to say, but what do you do if you have multiple converters? How do you handle multiple power supplies?

Henry says that you should keep one plane, and he prefers to call it a reference plane rather than a ground plane since most designs have a chassis common, not an earth ground. Then, he says, you should use component placement and routing discipline in order to keep the digital signals out of the analog circuits. He has presented some great work on how far away traces have to be for them to not interfere. It makes me love strip line buried between planes, rather than microstrip that can radiate out 12 times its width.-**by Paul Rako**

www.edn.com/anablog.For the full post, go to www.edn.com/081002b1.

# By every measure, Analog ICs mean better data in less time.

### **Our Latest Data Acquisition Innovations**

### Programmable Gain Instrumentation Amplifiers AD8250, AD8251, and AD8253

PGIAs offer unmatched speed and precision; require 75% less power and are up to 90% smaller than competing in-amps.

#### High Precision Dual Amplifier 0P2177

60  $\mu$ V maximum offset, 0.7  $\mu$ V/°C maximum drift, 8  $\mu$ V/ $\sqrt{Hz}$  typical low noise, and low power consumption for unmatched performance.

### 3-Channel, Low Noise, Low Power, 16-Bit and 24-Bit $\Sigma\text{-}\Delta$ ADCs AD7792 and AD7793

Complete AFEs for high precision measurement; on-chip amplifier allows direct interface of small amplitude signals to the ADC.

### 16-Bit, 10 MSPS, 92 dB SNR, 130 mW Power PulSAR $\ensuremath{^{\ensuremath{\otimes}}}$ ADC AD7626

Breakthrough performance enables faster, more precise data acquisition system designs.

### 14-Bit, 125 MSPS, 85 dBc SFDR, Low Power ADC AD9246

Combines excellent SFDR over a wide input bandwidth with low aperture jitter to accurately sample high frequency signals.

#### High Speed Digital Isolators ADuM140x

Compared to optocouplers, ADI's 4-channel digital isolators offer faster data rates, greater reliability with isolation ratings up to 2.5 kV, and up to 70% savings in board space.

analog is everywhere".

## See why more engineers want ADI experience inside their data acquisition designs.

Engineers working on data acquisition (DAQ) applications depend on Analog Devices to meet the demands of their designs and the expectations of their customers. We've taken our industry-leading data converters and amplifiers, added newly developed instrumentation components—such as high speed digital isolators and low jitter clocks—and optimized them for DAQ applications. The result is unmatched component functionality, reliability, and compatibility with proven specifications to shorten the design process and yield readings you can trust.

To learn more about what Analog Devices can do for your own world-class designs, order samples, or download data sheets, visit *www.analog.com/daq-ad1*.

## VOICES CriticalBlue's David Stewart

avid Stewart is founder and chief executive officer of CriticalBlue (Edinburgh, Scotland) and has more than 20 years' experience in the EDA and semiconductor industries, 10 of which he spent at Cadence Design Systems, where he was a founder and business-development director of the SOC (system-on-chip)-design facility at the Alba Campus in Scotland. This initiative attracted worldwide interest, and the design center grew to more than 200 people in its first 18 months. For an expanded version of the following interview, go to www.edn.com/ 081002p1.

## What are the challenges that your customers are now facing?

We straddle the hardware/software-development and -design boundaries, so we see customers on both sides. In a sense, there's one challenge right there, which has been identified for a number of years as a key issue in that hardware and software have typically been designed separately, and the two disciplines don't communicate well with each other. I don't think that problem has been solved yet, although it's better.

At a company level, what I see people challenged with is how to manage the necessary investment in building silicon platforms with getting the most out of those platforms. The biggest implication of that [challenge] is that these silicon platforms need to be a lot more programmable than they were before, so the increasing use of processors [is a concern], of course, but on top of that is layered the issue of power consumption, implying a smaller number of processing

elements working together to deliver the same performance at lower power consumption.

## How well has the industry dealt with this problem?

I don't think we have dealt with it. In many cases, particularly with respect to the multicore programming, we have expected some new panacea to suddenly appear, and there is a group of people who have been waiting for that to happen, and there are other people that are getting on with doing things.

What history has taught me is that engineers tend to grow in an evolutionary way; they don't tend to suddenly throw something away and start at the beginning. So, a brandnew approach is an interesting idea, but I don't see anybody with much appetite for implementing anything like that at this point because, specifically, when the markets are tough and people are being cautious ... people are much more likely to stick with what they know and try to evolve it than to throw everything away and

make a huge bet on something that's brand new.

## But will a new design be required in the future?

In an ideal world, that might be an interesting solution, but in terms of practically getting something that people might adopt, I struggle to find examples of where that's been done in the past. There aren't a lot of examples of brand-new things coming in and being adopted widespread across the industry; that's usually not what happens.

#### Are the multicore and hardware/software problems the same issues?

They are different issues. The issue of hardware/ software design is when you are building a base platform and you are trying to decide what to put on it, how to configure it, which pieces to put in hardware and which to put in software, and so on, and there are a lot of challenges with that [issue].

Then, you've got the people who are actually using the platforms—the end customers, if you like—who plan to program them and use them. And they are not designing hardware; they are purely interested in getting the best performance out of the platform they've been given and needing to learn about multicore-software programming in order to do that. There is a connection, but they are two different challenges.

#### What does CriticalBlue focus on in the multicore and hardware/software areas?

In the hardware/software area, we developed a technology to allow the direct migration of software functionality into a hardware coprocessor. So, in other words, we

developed a methodology that allows you to use software to design the hardware, which is something that doesn't really exist at this point.

In the multicore space, we've been doing a lot of work to help people analyze software that they have and figure out how to redeploy it on multicore architectures—for example, a single, standard RISC core and then multiple coprocessors. So, you might look at analyzing some software running on an ARM processor and what you need to do to that software to be able to put it onto multiple coprocessors as well as the ARM.

## What is CriticalBlue's approach to that issue?

We're focused very much on pragmatic solutions that help people work within the environments and the software codes that they already have, and it harks back to the point about whether we'll ever see a shiny new language in which everything can be captured and expressed. We may do, but we've certainly been working on the principle that we're going to stick with the existing languages and that people have a lot of existing software that they wish to be able to redeploy into these multicore architectures, and they need help with how to do that.-Interview conducted and edited by Ann Steffora Mutschler

# Signal processing ICs to help redefine what automobiles can be.

------

#### **Hybrid Electric Vehicle Systems**

Efficiency means economy. Increased vehicle range from high voltage batteries, electric motors, and power conversion is achieved through application specific Analog Devices ICs: resolver-to-digital transmission controllers, *i*Coupler® digital isolators, and other precision linear ICs.

#### Safety Systems

Protection provides confidence. Airbag and vehicle stability systems with added functionality are made possible with *i*MEMS<sup>®</sup> gyroscopes and accelerometers. Customized radar and lidar designs for adaptive cruise control, lane departure warning, and parking assist are enabled by ADI's converters, amplifiers, comparators, and PLL synthesizers.

#### Infotainment Systems

Enjoy the ride. High fidelity decoding, equalization, and filtering in audio systems are provided by SHARC<sup>®</sup> and SigmaDSP<sup>®</sup> processors, codecs, and amplifiers. Video amplifiers and encoders/decoders enhance displays and monitors. Blackfin<sup>®</sup> processors optimize software-defined radio, hands free communications, head unit control, and iPod<sup>®</sup> connectivity.

### Economical. Safe. Fun.

By offering the industry's most complete range of signal processing technologies and expertise, Analog Devices provides the functional building blocks engineers need to design safer, more enjoyable, and more environmentally friendly automobiles. We deliver ICs with industry-best functionality for concert hall quality audio, improved fuel economy, reduced emissions, advanced driver safety, comfort, and convenience.

ADI has earned a reputation for dependable IC performance and reliability in demanding applications—such as data acquisition, motor control, wireless infrastructure, and professional audio—and is applying this expertise to optimize ICs for automotive design.

To learn more about how Analog Devices' signal processing ICs are redefining the future of automobiles, visit *www.analog.com/auto-ad1*.

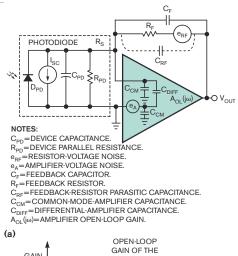

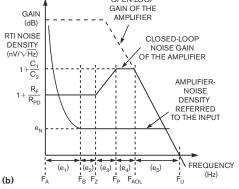

## Transimpedance-amplifiernoise issues

ow much noise is too much noise in a photodiode-preamplifier circuit? You can derive the noise performance of a transimpedance amplifier (Figure 1a) with calculations or by using a Spice simulation (Reference 1). When calculating the noise performance of the circuit, consider six regions in the frequency spectrum (Figure 1b)

and add each region with a root-sum-square equation or the following equation (Reference 2):

$$V_{OUT}(NOISE_{RMS}) = \sqrt{e_1^2 + e_2^2 + e_3^2 + e_4^2 + e_5^2 + e_{RF}^2}.$$

The first five regions are equal to the multiple of the areas under the closed-loop-gain and amplifier-noise-density curves. The area under the noise-density curve in the  $e_1$ , flicker-noise (1/f), region is  $V_{1/f:fB-fA} = A_N \sqrt{\ln(f_B/f_A)}$ , where  $A_N$  is the amplifier's input-noise-density at 1 Hz and  $f_B$  is the corner frequency where the flicker noise tapers off. For many CMOS or FET amplifiers, the flicker-noise region usually ranges from dc to 100 or 1000 Hz. A calculation proves that the contribution to noise in this low-frequency region is relatively low:

$$\mathbf{e}_1 = (1 + \mathbf{R}_F / \mathbf{R}_{PD}) \times \mathbf{A}_N \times \sqrt{\ln(\mathbf{f}_B / \mathbf{f}_A)},$$

where  $R_{\rm F}$  is the feedback resistor and  $R_{\rm PD}$  is the device's parallel resistance.

In the  $e_2$  region, multiply the broadband noise of the amplifier, the closedloop dc-noise gain  $(1+R_F/R_{PD})$ , and the square root of the region's bandwidth. Again, the contributed noise in this region is usually relatively low because of its location in the lower frequency range.

$$\mathbf{e}_2 = (1 + \mathbf{R}_F / \mathbf{R}_{PD}) \times \mathbf{e}_N \times \sqrt{\mathbf{f}_P - \mathbf{f}_Z}.$$

Calculate the noise contribution and the e<sub>3</sub> region in the same manner with  $f_p=1/[2\pi(R_{pD}||R_F) (C_{pD}+C_{CM} + C_{DIFF}+C_F+C_{RF})]$  and  $f_z=1/[2\pi(R_F) (C_F+C_{RF})]$ .

$$e_3 = (1 + R_F / R_{PD}) \times e_N \times (1 H_z / f_7) \times \sqrt{f_P / 3 - f_7 / 3},$$

where  $C_{PD}$  is the device's capacitance and  $C_{DIFF}$  is the differential amplifier's capacitance.

The noise in regions  $e_4$  and  $e_5$ uses the higher-frequency gain of the closed-loop-gain curve with the value of  $C_1$  being the parallel combination of the input capacitors, or  $[C_{p-R1}||2C_{CM}||C_{DIFF}]$ , and  $C_2$  is the parallel combination of  $C_F$  and  $C_{RF}$

$$e_{4} = (1 + C_{1}/C_{2}) \times e_{N} \times \sqrt{f_{AOL} - f_{P}}$$

$$e_{5} = (1 + C_{1}/C_{2}) \times e_{N} \times \sqrt{\pi \times (f_{L} - f_{AOL})/2}.$$

The sixth part of the noise equation,  $e_{c}$ , represents the noise contribution of the feedback resistor. The amplifier does not gain the contribution of noise from the feedback resistor:

$$\mathbf{e}_6 = \sqrt{4 \times \mathbf{K} \times \mathbf{T} \times \mathbf{R}_F \times (\mathbf{BW})},$$

where K is Boltzmann's constant, which is  $1.38 \times 10^{-23}$ ; T is temperature

in Kelvin;  $R_F$  is the feedback resistor in ohms; and BW is the bandwidth of interest.

When asking how much noise is too much noise in this photodiode-preamp circuit, consider that a 12-bit system operating with a 5V input range has an LSB of 1.22 mV. The LSB for a 16-bit system with the same inputvoltage range is 76.29  $\mu$ V. Both LSBs are peak-to-peak numbers, and the values in this column are root-meansquare values (**Reference 3**).EDN

Bonnie Baker is a senior applications engineer at Texas Instruments. She can be reached at bonnie@ti.com.

+ For a list of the references cited in this column, go to www.edn.com/081002bb.

## Design with the best: High Performance Analog

ANALOG AVAGO FAIRCHILD

ON Semiconductor ON Semiconductor

"On-time delivery with no minimum fees. *That's important.*

Online access to all my current and past orders.

That's important, too.

The best analog brands. *That's critical.*"

LINEAR TECHNOLOGY LTM8021 DC/DC Switchmode µModule Regulator. Tiny package creates space by mounting on back of board.

intersil

### Design with the best brands

You'll find the best components and the best information in one site. Visit <u>www.newark.com/instrumentation</u> to make the most of the newest advances in high performance processing, high performance analog, power supplies, imaging, connectors, discretes and passives.

Find more at www.newark.com and 1.800.4.NEWARK

A Premier Farnell Company

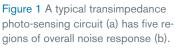

## Artificial cochlea: an example of structural processing

he cochlea is the portion of the inner ear that senses sound vibrations and converts them into electrical signals that the auditory system can interpret. The cochlea is an example of active cellular mechanical forcing and structural processing in which the shape and physical composition of the sensory organ work in combination to accomplish a complex transform. In this case, the cochlea separates a sensed, complex sound wave into its basic frequency components.

The cochlea is a curled structure, which is filled with fluid that moves in response to the vibrations coming through the oval window from the middle ear. Along the length of the cochlea are thousands of hairs that are set in motion in the liquid at the resonance points of the incoming sound wave. Each hair, based on its position within the cochlea, essentially isolates and detects a frequency band. This task is much like performing an FFT (fast Fourier transform) on a sound wave received on a conventional microphone but without performing the digital computations of the FFT (courtesy Zina Deretsky, National Science Foundation).

### this article at www.edn.com/ 081002pry.

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

**PRY FURTHER AT EDN.COM**

+ Read an expanded version of

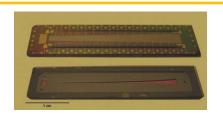

Current state-of-the-art technology for an artificial cochlea operates in a similar fashion except that, unlike the tightly curled cochlea, the MEMS (microelectromechanical-system)-based cochlea stretches out in a linear structure. The 3-cm-long device comprises an acoustic input port at the narrow end of a tapered strip. Where the strip is narrow, the sense material is stiff and vibrates in response to high-frequency compression waves in the fluid that the strip is immersed in. Additionally, as the strip widens, the material is more compliant, vibrates more easily, and absorbs the energy of lower-frequency waves (courtesy Karl Grosh, University of Michigan, and Robert White, Tufts University).

Earlier versions of the micromechanical cochlea used a capacitive-sensing approach, but the development team is working with piezoelectric sensing that takes better advantage of lithography and etching techniques. Although the structure of the cochlea passively separates a sound wave into its components' resonance points, the act of sensing the resonance points and converting them into a usable signal is an active process. The current implementation of the artificial cochlea relies on a cantilever-beam structure in which each beam is supported on only one end and the free end of the beam can sense motion of the micromechanical cochlea. This image shows sets of cantilevers that could be used for this purpose and integrated directly into the fabrication of the artificial cochlea. The pictured devices were fabricated to make many thousands of piezoelectric MEMS microphones. This technology was co-opted for the purpose of a cochlear sensor (courtesy Karl Grosh, University of Michigan).

## "How can I tell if a power supply is reliable?"

## There's an indicator on the front.

It says "Agilent." With a typical MTBF of 40,000 hours, over half-a-century of experience, and with more than 250 models to choose from, Agilent's power supplies are the ones you can count on. In fact the array of our power supplies is so extensive, it wouldn't fit on this page. For clean, low-noise, programmable power to countless DUTs, there's an Agilent power supply with your name on it. Actually, it's our name on it, but you know what we mean.

For three measurement tips and the entire Agilent Power Products Brochure go to www.agilent.com/find/powertips

u.s. 1-800-829-4444 canada 1-877-894-4414

## From quote to delivery, we've pioneered online PCB ordering.

"Sunstone has done a great job with all of our orders. We rely on your easy online ordering system, quality boards, and fast lead times."

- Sunstone customer feedback

$\bigcirc$  $\bigcirc$  $\bigcirc$

2-6 layer, quickturn proto-boards

Complete customer service, 24/7, 365 days a year

Over 30 years of manufacturing experience

The ultimate in easy online PCB ordering

Visit us at WWW.SUNSTONE.COM

HIGH-SPEED GRAPHICS, USER INTER-FACES, AND NETWORKS REPRESENT THE NORM IN EMBEDDED-SYSTEM DESIGNS, AND THESE PERFORM-ANCE ISSUES DICTATE THE USE OF MULTITASKING FIRMWARE.

## ON TIME, EVERY TIME: EMBEDDING REAL-TIME PERFORMANCE

BY WARREN WEBB • TECHNICAL EDITOR

s a new generation of computer-savvy users and gamers becomes your primary embeddeddevice customer, responsiveness and real-time performance become critical evaluation issues. Systems must manage priorities and tasks to provide nearly instantaneous response to users, external events, and the network. To meet these requirements, commercial vendors and the open-source community offer dozens of

ready-to-run or customizable software packages ranging from minimal-resource kernels to full-featured RTOSs (real-time operating systems). Before you settle on an approach, however, it is important to analyze the inner workings of a candidate package to make

the right match for your application. Scheduling algorithms, task synchronization, resource requirements, memory allocation, latencies, add-on modules, certifications, security, multicore options, and development-tool support are a few of the real-time functions and features that can make or break your design.

Real-time systems automatically execute software routines or tasks in response to external or timing events. Most embedded RTOSs are pre-emptive by design so that a task can suspend any lower-priority routines and gain control of the processor until the higher-priority task completes or until an even higherpriority task pre-empts the previous task. Unlike so-called soft real-time platforms, which simply list an average length of time to start the routine, most critical embedded operating systems must be deterministic so that they guarantee that tasks start within a precise length of time after an external event. The basic architecture of a typical multitasking RTOS for embedded devices includes a program interface, the kernel, device drivers, and optional service modules.

The kernel is the core of the realtime software and includes an interrupt processor, a scheduler, resource-sharing flags, and memory management. One of the kernel's primary functions is to handle interrupts that external or internal events cause. As interrupts take place, the processor transfers control to a service routine that logs in the event, sends a message to the scheduler, and returns to the active code. The scheduler establishes the execution order of each task based on its priority and saves execution information for each interrupt. In addition to priority scheduling, a realtime kernel also provides flags for task synchronization. For example, if several tasks want to use a data resource at once, a flag or semaphore locks the resource to a single task until the transfer is complete.

The kernel design is also important in minimizing the latencies that can degrade the performance of a real-time system. Interrupt latency is the worst-case delay between an external event, such as a switch closure, and the first instruction of the interrupt routine. If you enable the processor interrupts, the hardware delay is only nanoseconds long, but it can vary from processor to processor. The processor needs to complete only the current instruction before jumping to the requested interrupt location. If the processor has only one interrupt line, the time to poll inputs determines which interrupt routine to call as part of the interrupt latency. Another latency that the kernel contributes is the time it takes to switch between tasks. Each task has a program counter, a data-area

Figure 1 The XPedite5370 single-board computer from Extreme Engineering Solutions provides designers with boardsupport software for the major real-time operating systems.

#### AT A GLANCE

Critical embedded operating systems must be deterministic to guarantee that tasks start within a precise length of time after an external or timing event.

The kernel is the core of a realtime operating system and includes an interrupt processor, a scheduler, resource-sharing flags, and memory management.

Add-on modules, such as security, safety, networking, and a GUI (graphical user interface), must work concurrently without disrupting RTOS (real-time-operating-system) performance.

An RTOS-aware softwaredevelopment-tool chain simplifies firmware debugging and real-timeperformance analysis.

pointer, register data, and other state information that the processor must save for the current task and restore for the pre-empting task.

RTOS designers usually include a variety of optional modules and drivers outside the kernel to attract more users and to ensure that the combined package meets the advertised performance specifications. For example, almost every RTOS includes communications protocols, such as TCP/IP (Transmission Control Protocol/Internet Protocol), and most of the major RTOS vendors also offer GUI (graphical-user-interface) routines. Users can add or delete these modules depending on the application. Green Hills Software offers the Integrity RTOS in multiple configurations targeting embedded-system applications, including aerospace, automotive, medical, secure networking, wireless, and software-defined radio. These preconfigured packages integrate the most common modules and drivers into a series of off-the-shelf platforms. Product-development licenses for the Integrity RTOS start at \$15,000 for a singleuser enterprise license, with no royalty fees for runtime deployment.

If your application requires serious data processing or distributed processors, you should investigate an RTOS that targets use with multiple processors. You can spread tasks across several processors to gain a significant performance boost; however, all tasks must be in constant communication to maintain deterministic behavior. For example, the high-performance Enea Embedded Technology OSE (operating-system environment) targets use with highavailability, high-reliability distributed systems, such as those in telecommu-

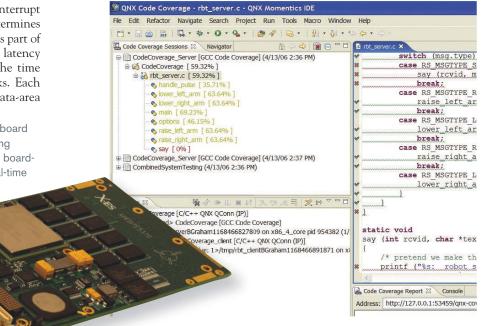

Figure 2 The Momentics development suite from QNX Software Systems provides a collection of productivity-and-analysis tools for the Neutrino RTOS in a single Eclipse-based IDE.

## See the bigger picture...

with feature-rich tools for debugging mixed signal designs.

MSO4000 Series Mixed Signal Oscilloscopes Performance Specifications

| Models                           | MS04032, MS04034, MS04054, MS04104                            |

|----------------------------------|---------------------------------------------------------------|

| Bandwidth                        | 1 GHz, 500 MHz, 350 MHz models                                |

| Channels                         | 2 or 4 analog and 16 digital                                  |

| Record Length                    | 10 M points on all analog and digital channels                |

| Sample Rate                      | Up to 5 GS/s (analog) / Up to 16.5 GS/s (digital)             |

| Display                          | 10.4 in. (264 mm) XGA                                         |

| Serial Bus Trigger<br>and Decode | I <sup>2</sup> C, SPI, RS-232/422/485/UART, CAN, LIN, FlexRay |

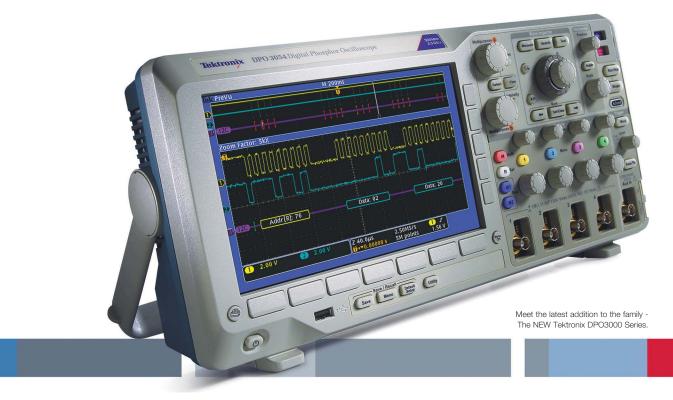

See more. Try the virtual product demo at: www.tektronix.com/bigpicture

|    | DPO4000 Series Oscilloscopes<br>Performance Specifications |                                                 |  |  |  |  |  |

|----|------------------------------------------------------------|-------------------------------------------------|--|--|--|--|--|

| M  | odels                                                      | DP04104, DP04054, DP04034                       |  |  |  |  |  |

| Ba | andwidth                                                   | 1 GHz, 500 MHz, 350 MHz models                  |  |  |  |  |  |

| Cł | nannels                                                    | 4 analog                                        |  |  |  |  |  |

| Re | ecord Length                                               | 10 M points on all channels                     |  |  |  |  |  |

| Sa | ample Rate                                                 | Up to 5 GS/s on all channels                    |  |  |  |  |  |

| Di | splay                                                      | 10.4 in. (264 mm) XGA                           |  |  |  |  |  |

|    | erial Bus Trigger<br>Id Decode                             | PC, SPI, RS-232/422/485/UART, CAN, LIN, FlexRay |  |  |  |  |  |

| NEW! DPO3000 Series Oscilloscopes<br>Performance Specifications |                                                             |  |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Models                                                          | Models DP03054, DP03052, DP03034, DP03032, DP03014, DP03012 |  |  |  |  |

| Bandwidth                                                       | 500 MHz, 300 MHz, 100 MHz models                            |  |  |  |  |

| Channels                                                        | 2 or 4 analog                                               |  |  |  |  |

| Record Length                                                   | 5 M points on all channels                                  |  |  |  |  |

| Sample Rate                                                     | 2.5 GS/s on all channels                                    |  |  |  |  |

| Display                                                         | 9 in. (229 mm) WVGA widescreen                              |  |  |  |  |

| Serial Bus Trigger<br>and Decode                                | PC, SPI, RS-232/422/485/UART, CAN, LIN                      |  |  |  |  |

See more and solve faster with Tektronix DPO and MSO Series oscilloscopes. This feature-rich family of oscilloscopes, with bandwidths up to 1 GHz, have the power and functionality to help make your work easier. With Wave Inspector® you can easily search and navigate through uncompromised long records; and large, high-resolution displays let you clearly see all on-screen data and catch glitches you might otherwise have missed. Combine this with integrated serial trigger, decode and search, and you will be debugging mixed signal designs faster and easier than ever before.

nications networks. A recently updated Linx feature adds priority messaging to maintain interprocess communications in systems that become congested due to a fault condition. Prices for the Enea OSE start at \$8000 for a single developer's seat, and Linx is available for prices starting at \$5000 for a multiuser license.

One way to eliminate surprises with real-time hardware integration is to base your embedded design on COTS (commercial-off-the-shelf) modules that include preconfigured support software. For example, Extreme Engineering Solutions recently introduced the XPedite5370 single-board computer featuring board-support packages for the Wind River VxWorks, QNX Neutrino, and Green Hills Integrity RTOSs (Figure 1). Extreme Engineering based the 3U, VITA (VMEbus International Trade Association) 46-compliant module on Freescale Semiconductor's MPC8572E PowerQUICC (quad-integrated-communications-controller) III dual-core processor, and the device supports highspeed fabric interconnections over PCIe

+ For more on free software for embedded design, go to www.edn.com/ article/CA6582852.

Read another article about embedded Linux at www.edn.com/article/ CA450620.

+ Go to www.edn.com/081002df and click on Feedback Loop to post a comment on this article.

+ For more feature articles, go to www.edn.com/features.

### THE SMARTER WAY TO DESIGN A SMARTPHONE

#### By Todd Brian, Mentor Graphics

Today, manufacturers of electronic devices face challenges that they never have before. Take the example of a mobile phone. Beyond its primary function of making a call, it must also seamlessly manage documents, such as e-mail, files, and video; have an easy-to-use GUI (graphical user interface); and be able to access and exchange data over wireless or cellular networks. All of these different yet interrelated technologies must combine to offer a homogeneous user experience. And, to satisfy demanding consumers, the latest model must reach the market within an 18month window and at mass-market cost. How can designers balance this trade-off of features, performance, and cost?

Enter the operating-system software. Whether inside a sleek mobile phone or another multimedia device, the operating system must retain the characteristics of an embedded operating system: efficiency, scalability, determinism,

and speed. Unlike the RTOS (real-time operating system) of vesterday, however, today's embedded operating-system platform must provide a complete foundation for cost-efficient innovation at the device level. Look under the hood of any mobile phone, and you will find that it relies on a set of basic technologies, such as connectivity, file storage, graphics, and all the drivers for the peripheral hardware. **Those functions require** a lot of software. From a device manufacturer's standpoint, this software is costly to develop and maintain in-house, yet it does not differentiate a device in the market.

A better approach is to start with a full-featured operating system containing the latest in networking and connectivity, file-storage, and USB (Universal Serial Bus) capabilities. This operating-system platform must also include the latest technology in graphics/multimedia and

support industry APIs (application-programming interfaces), such as the **OpenMax specification** from the Khronos Group. For devices that do not comply with OpenMax, the multimedia framework can still exploit codec support and provide a common interface to the application layer. **OpenMax also delivers** hardware integration of other graphical and multimedia capabilities and XML (Extensible Markup Language)-driven menus. Furthermore, a cost-efficient RTOS platform must enable applicationsoftware development, whether by in-house teams or by independent software providers. Integral to the platform is a robust development platform, including an IDE (integrated development environment), a compiler, a debugger, and a profiler and simulation environment. Chip-set vendors or device manufacturers can extend and package this tool suite as a devicespecific SDK (softwaredevelopment kit). The next-generation operating system must work with various embedded applications. Much like a custom-tailored suit, every line of code on the device is there explicitly due to the design of the device, and manufacturers can easily extend and customize those lines so that the RTOS environment is an exact fit.

Average consumers may be relatively unaware of the operating system inside their mobile phones. Obscure as it may be, however, it is this nextgeneration RTOS platform that enables better economics of mobile phones and other electronic devices and enables device manufacturers to quickly deliver the latest features to their customers.

### AUTHOR'S BIOGRAPHY

Todd Brian is productmarketing manager at the embedded-systems division of Mentor Graphics. You can reach him at todd\_brian@mentor.com.

### The power of the industry's broadest product portfolio.

## ON Semiconductor now has the industry's broadest selection of power efficient solutions—your single source for everything from ASICs and ASSPs to standard ICs and discrete components.

When it comes to power efficient solutions, ON Semiconductor is the one name to know. In addition to providing a wide variety of discrete components and standard integrated circuits, ON Semiconductor now also offers specialized solutions like custom ASICs, ASSPs, and power efficient GreenPoint<sup>™</sup> reference designs. No matter what your application is—ranging from medical to automotive and industrial to power supplies, and everything in between—ON Semiconductor is the only resource you can be sure has a solution that's complete, effective, and efficient. Now that's powerful.

GreenPoint is a trademark of SCILLC. All other brand names and logos are registered trademarks or trademarks of their respective holders.

Find your next power solution at www.onsemi.com/thepower

**ON Semiconductor®**

## Terabyte RF Instruments

## Use Real-World Data to Create Better Designs

Take advantage of more than 5 hours of continuous RF spectrum to characterize your components. With record and playback tools from National Instruments, you can:

- Capture and generate RF signals up to 2.7 GHz

- Stream 20 MHz instantaneous bandwidth

- Store and retrieve hours of data on a 2 TB RAID drive

>> Watch product demonstrations and download complete specifications at ni.com/streaming/rf

### 800 891 8841

©2008 National Instruments Corporation. All rights reserved. National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2008-9209-101-D (peripheral-component-interconnect express), Serial Rapid I/O, and GbE (gigabit Ethernet). Prices for the XPedite5370 start at less than \$8000, and volume discounts are available.

Certifications are another way to ensure that an RTOS meets some or all of your performance requirements. For example, Wind River Systems claims that its VxWorks operating system was the first to receive certification for conformance to the POSIX (portable-operating-system-interface) PSE52 real-timecontroller 1003.13-2003 product standard. POSIX comprises a family of related IEEE standards that define the API (application-programming interface) and critical performance areas. In addition to ensuring source-code portability, PSE52 certification confirms that the RTOS delivers the predictable response times that time-critical applications require.

The development-tool chain is another big issue in the selection of an RTOS. You will spend most of your software-development and -debugging efforts interacting with the IDE (integrated development environment) to gain quick access to the editor, compiler, linker, downloader, and runtime tools. The open-source Eclipse IDE has become a popular and easy-to-use standard interface for embedded-softwaretool vendors. The platform allows users to easily create custom Eclipse configurations because everything other than a small runtime kernel is a plug-in. For example, the Momentics tool suite from QNX Software Systems provides a set of productivity-and-analysis tools for the Neutrino RTOS, all integrated into a single Eclipse-based IDE (Figure 2).

If you decide on a commercial-software package, you must also determine whether you need or want to purchase the source code for the vendor's RTOS. Some vendors automatically supply the source code when you purchase their software, whereas others charge extra. With the source code, you have the option to tweak the vendor's software to remove every line of unused code and reclaim vital memory space. The source code can also help you understand those subtle bugs in your application code. However, vendors that supply only object code claim that, if you change the source code, you have created a unique and unsupportable RTOS. You can alREAL-TIME SYSTEMS ARE CRITICAL IN MANY APPLICATIONS, AND A MISSED DEAD-LINE CAN RESULT IN CATASTROPHIC LOSS OF LIFE OR PROPERTY.

ways purchase a copy of the source code to document your system or to deliver to your customer.

Embedded devices come in all sizes and capabilities, but one thing is for sure: As the software complexity grows, the need for real-time, deterministic performance becomes vital (see sidebar "The smarter way to design a smartphone"). In fact, real-time systems are critical in many applications, and a missed deadline can result in catastrophic loss of life or property. As an embedded-system designer, you can expect your customers to ask for higher performance and increased complexity as the technology bubble expands. Fortunately, a huge group of software vendors and open-source volunteers are already working on the next generation of real-time firmware to simplify your next embedded-software application.EDN

#### FOR MORE INFORMATION

Enea Embedded Technology www.enea.com Extreme Engineering Solutions www.xes-inc.com Freescale Semiconductor www.freescale.com Green Hills Software www.ghs.com Khronos Group www.khronos.org Mentor Graphics www.mentor.com QNX Software

Systems www.qnx.com VITA (VMEbus International Trade Association) www.vita.com

Wind River Systems www.wrs.com

You can reach Technical Editor

at 1-858-513-3713 <u>and wwebb@edn.com</u>.

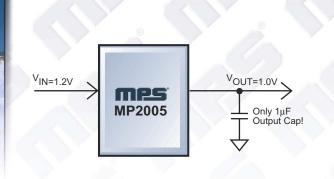

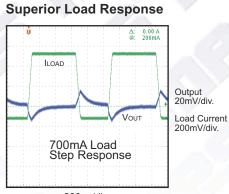

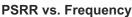

## Highest Speed, µPower ULDO Delivers 48dB (1MHz) PSRR!

800mA Load Current & Superior Transient Response

200µs/div.

- High PSRR: 65dB (1kHz), 48dB (1MHz)

- Stable with 1µF output capacitor

- 100µA Supply Current

- Ultra-low dropout voltage: <90mV</p>

- Wide input voltage range: 1.0V to 5.5V

- Adjustable Vout range: 0.5V to 4.0V

| MPS Precision LDO Family |               |          |              |          |              |            |  |  |  |

|--------------------------|---------------|----------|--------------|----------|--------------|------------|--|--|--|

| Part                     | Dropout       | Max Iout | VIN Range    | Min Vout | Adj or Fixed | Package    |  |  |  |

| MP2000                   | 250mV (100mA) | 150mA    | 1.35V - 6.0V | 0.5V     | Adj          | TSOT23-5   |  |  |  |

| MP8801                   | 150mV (150mA) | 150mA    | 2.7V - 6.5V  | 1.25V    | Adj/Fixed    | TSOT23-5   |  |  |  |

| MP8802                   | 230mV (250mA) | 250mA    | 2.7V - 6.5V  | 1.25V    | Adj/Fixed    | TSOT23-5   |  |  |  |

| MP2002                   | 290mV (500mA) | 500mA    | 1.35V - 6.5V | 0.5V     | Adj          | QFN8 (2x3) |  |  |  |

| MP89046                  | 360mV (600mA) | 600mA    | 2.5V - 6.5V  | 0.5V     | Adj          | QFN8 (2x3) |  |  |  |

| MP2005                   | <90mV (800mA) | 800mA    | 1.0V - 5.5V  | 0.5V     | Adj          | QFN8 (2x3) |  |  |  |

DC to DC Converters CCFL / LED Drivers Class D Audio Amplifiers Linear ICs

NEV

# VIRTUALIZATION:

**BY BRIAN DIPERT • SENIOR TECHNICAL EDITOR**